Memtest86 Pro v10.7.1000 ISO-USB Multilingual

MemTest86 Pro is a powerful memory diagnostic software tool designed to test the reliability and stability of computer memory. Developed by PassMark Software, MemTest86 Pro is widely recognized as one of the most accurate and comprehensive memory testing utilities available today.

At its core, MemTest86 Pro is a program that runs a series of tests on a computer’s RAM (random access memory) chips in order to identify any potential errors or faults that may exist. These tests are designed to thoroughly examine the memory subsystem of a computer, including the RAM modules, the motherboard’s memory controller, and the CPU’s integrated memory controller.

One of the key features of MemTest86 Pro is its ability to detect even the most subtle memory errors that can go unnoticed by other diagnostic tools. The program uses several advanced algorithms and techniques to perform a deep analysis of the system memory, including exhaustive bit-level analysis, pattern tests, and data integrity checks.

In addition to its comprehensive testing capabilities, MemTest86 Pro also includes a range of powerful reporting and logging features, enabling users to easily track and analyze the results of their memory tests over time. Test results can be saved to disk or printed out for further analysis, making it easy to identify patterns or trends in memory errors over time.

Another notable feature of MemTest86 Pro is its support for UEFI firmware, which enables the program to boot directly from modern UEFI-based systems without the need for legacy BIOS emulation. This allows users to run memory tests on the latest hardware platforms using the most up-to-date firmware interfaces.

MemTest86 Pro also supports a variety of different memory architectures and technologies, including DDR4, DDR3, DDR2, and DDR SDRAM, as well as ECC and non-ECC memory modules. This broad compatibility ensures that the program can be used with a wide range of computer systems, from consumer-grade desktops and laptops to high-end enterprise servers.

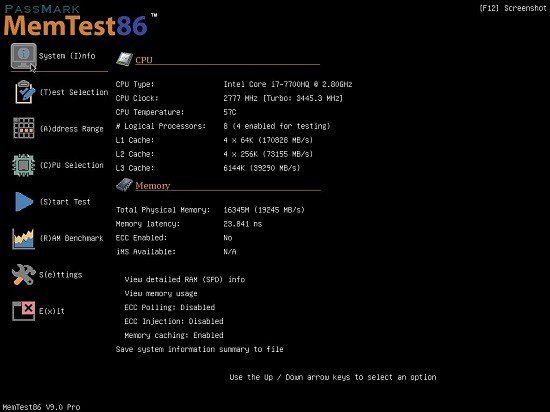

To use MemTest86 Pro, users simply need to download the program and create a bootable USB drive, which can then be used to boot the system directly into the memory testing environment. The program includes an easy-to-use graphical user interface that guides users through the testing process step-by-step, making it accessible even to beginners.

In conclusion, MemTest86 Pro is a powerful and versatile memory diagnostic tool that provides users with a comprehensive set of features for testing the reliability and stability of computer memory. Its advanced algorithms, support for modern UEFI firmware, and broad compatibility with different memory architectures and technologies make it a go-to choice for system administrators, IT professionals, and power users alike. Whether you’re looking to troubleshoot a specific issue with your computer’s memory or simply want to ensure that your system is running at peak performance, MemTest86 Pro is an essential tool for any serious computer user.

There are many good approaches for testing memory. However, many tests simply throw some patterns at memory without much thought or knowledge of memory architecture or how errors can best be detected. This works fine for hard memory failures but does little to find intermittent errors. BIOS based memory tests are useless for finding intermittent memory errors.

RAM chips consist of a large array of tightly packed memory cells, one for each bit of data. The vast majority of the intermittent failures are a result of interaction between these memory cells. Often writing a memory cell can cause one of the adjacent cells to be written with the same data. An effective memory test attempts to test for this condition. Therefore, an ideal strategy for testing memory would be the following:

- Write a cell with a zero.

- Write all of the adjacent cells with a one, one or more times.

- Check that the first cell still has a zero.

It should be obvious that this strategy requires an exact knowledge of how the memory cells are laid out on the chip. In addition there are a never ending number of possible chip layouts for different chip types and manufacturers making this strategy impractical. However, there are testing algorithms that can approximate this ideal and MemTest86 does just this.

The standard for memory diagnostics

– Boots from a USB flash drive to test the RAM in your computer for faults.

– Utilizing algorithms that have been in development for over 20 years.

Unreliable RAM can cause a multitude of problems. Corrupted data, crashes and unexplained behaviour.

Bad RAM is one of the most frustrating computer problems to have as symptoms are often random and hard to pin down. MemTest86 can help diagnose faulty RAM (or rule it out as a cause of system instability). As such it is often used by system builders, PC repair stores, overlockers & PC manufacturers.

PassMark MemTest86 supports all current technologies:

– 13 different RAM testing algorithms – including row hammer fault detection*

– All RAM types supported (DDR2, DDR3, DDR4, SODIMM, XMP, ECC)

– Self-booting off USB or Network (PXE)* boot, without needing DOS, Linux nor Windows

– Optimized for UEFI-based x86/ARM systems

– Native 64-bit code (since version 5)

– ECC error detection & injection*

– Secure Boot verified – Code signed by Microsoft

– Graphical interface with mouse input

– Save logs and create customizable HTML reports

– Full test automation via configuration file

– Support for memory blacklisting in Windows (badmemorylist) and Linux (BADRAM)

– Multi-language support (Chinese, German, Russian, Spanish & more)

MemTest86 Features:

UEFI

The new graphical standard for BIOS

Network (PXE) boot

Scalable, disk-less provisioning from a PXE server

Reports / Logs

Save results to disk

Self-booting USB

No O/S required

All RAM types supported

DDR2 / DDR3 / DDR4 / SODIMM / XMP / ECC

Foreign language support

Chinese, German, Russian, Japanese & more

Graphical interface

And mouse support

13 algorithms

Including SIMD and row hammer tests

Secure boot signed

Code integrity verified by Microsoft

What’s NEW:

Fixes/Enhancements

- Preliminary support for obtaining memory settings for Intel Core chipsets:

- 2nd gen (Sandy Bridge)

- 3rd gen (Ivy Bridge)

- 4th gen (Haswell)

- 5th gen (Broadwell)

- 6th gen (Skylake)

- 7th gen (Kaby lake)

- 8th gen (Coffee Lake)

- 9th gen (Coffee Lake Refresh)

- 10th gen (Comet Lake/Ice Lake)

- 11th gen (Rocket Lake/Tiger Lake)

- 12th gen (Alder Lake)

- 13th gen (Raptor Lake) Core chipsets

- Preliminary support for obtaining memory settings for Intel Core Ultra chipsets:

- 1st gen (Meteor Lake)

- 2nd gen (Arrow Lake)

- Lunar Lake

- Preliminary support for obtaining memory settings for Intel Xeon scalable chipsets:

- 1st gen (Skylake-SP)

- 2nd gen (Cascade Lake-SP)

- 3rd gen (Ice Lake-SP)

- 4th gen (Sapphire Rapids-SP)

- 5th gen (Emerald Rapids-SP)

- Preliminary support for obtaining memory settings for Intel Atom X Series (Elkhart Lake) chipsets

- Preliminary ECC support for the following Intel chipsets:

- 10th gen core (Ice Lake)

- 1st gen core ultra (Meteor Lake)

- 5th gen Xeon scalable (Emerald Rapid)

- Atom X Series (Elkhart Lake)

- Preliminary support for module decoding for Intel 10th gen core (Ice Lake) chipsets

- Added support for reporting various ECC error types (eg. IBECC/Scrub)

- Fixed rounding of DDR5 latency timings

- Fixed offsetted temperatures for AMD 19h family chipsets

- Suppress CPU errors due to UEFI firmware issues once already displayed

- Display “SPD FAIL” block error message when SPDMATCH check fails after test completion

- Updated localization strings (courtesy of Nagisa)

- Updated ImageUSB to v1.5.1006

- Updated blacklist

- Preliminary support for obtaining memory settings for Intel Core chipsets: